今年以来,全球半导体产业进入新的转折期,在新一轮的科技革命中,全国各方正在呼吁通过充分的发挥知识产权制度供给和技术供给的双重作用,进一步健全专利转化运用工作机制,大力推动专利产业化。

从专利方面看,全国半导体各路“英雄豪杰”正在加速破局。近日,华虹宏力、北方华创、芯联集成、积塔半导体、粤芯半导体、国科微、忆芯科技、摩尔线程等许多企业纷纷向外公布了一项项已授权的专利,旨在为半导体产业提供攻克技术壁垒的方案。

据天眼查信息,近日,上海华虹宏力半导体制造有限公司(以下简称“华虹宏力”)两项专利技术获得授权。

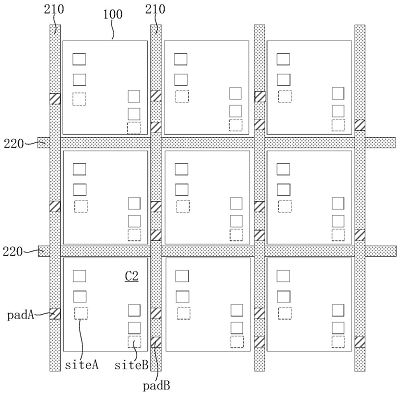

其中,一项名为“用于晶圆芯片并行测试的模拟量测试焊盘排布结构”专利,授权公告号为CN112147487B,授权公告日为2024年7月23日,申请日为2020年9月25日。

本申请涉及晶圆测试领域,具体涉及一种用于晶圆芯片并行测试的模拟量测试焊盘排布结构。所述晶圆包括若干个呈阵列式分布芯片,相邻芯片之间形成划片槽;相邻两列芯片之间形成纵向划片槽,相邻两排芯片之间形成横向划片槽;位于各个所述芯片周围的划片槽中,设有模拟量测试焊盘,所述模拟量测试焊盘与对应芯片电性耦合。

本申请通过将模拟量测试焊盘设于对应芯片周围的划片槽中,在节省焊盘占用芯片面积的同时,通过保证在进行晶圆测试时所述模拟量测试焊盘与对应芯片电性耦合,即能确保在晶圆芯片模拟参数并行测试的过程正常进行。

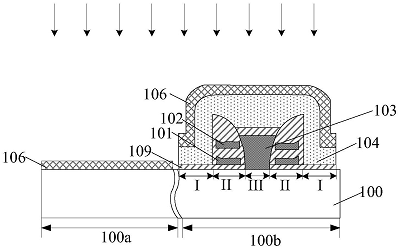

另一项名为“半导体结构的形成方法”,申请公布日为2024年7月23日,申请公布号为CN118382298A。

根据介绍,本发明提供一种半导体结构的形成方法,包括:提供衬底,所述衬底包括逻辑区和存储区,所述存储区包括字线区;在所述存储区上形成初始字线栅层;在所述初始字线栅层的顶部表面和所述逻辑区的所述衬底的表明产生初始栅氧层;对所述初始栅氧层进行热氧化处理,形成栅氧层,所述初始字线栅层表面的所述栅氧层的厚度大于所述逻辑区的所述衬底表面的所述栅氧层的厚度;在所述逻辑区的所述栅氧层的表明产生栅极层;刻蚀去除所述存储区的所述栅氧层以及所述栅氧层底部的部分所述初始字线栅层,在所述字线区的表明产生字线栅层,在形成字线栅层的过程中,栅氧层作为硬掩膜层,由于初始字线栅层表面的栅氧层的厚度变厚,从而在刻蚀的过程中能够表现出很好的阻挡性和稳定能力,来保证字线栅层的高度,提升字线栅层的高度均匀性,并且增加了字线区刻蚀的窗口,能够更好的降低编程串扰失效,具有较广泛的使用范围。

近日,北京北方华创微电子装备有限公司有两项专利获得了授权:一种集成电路的制造工艺、晶圆卡盘和晶圆加工方法。

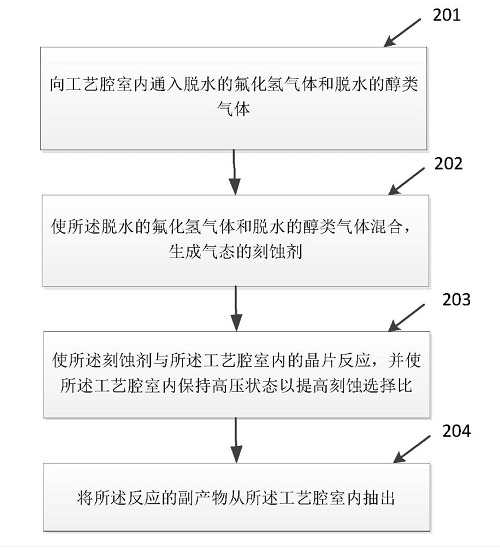

其中,“一种集成电路的制造工艺”专利,授权公告号为CN113506731B,授权公告日为2024年7月23日,申请日为2016年10月8日。

公开了一种集成电路的制造工艺,包括:去除晶片上的二氧化硅的方法,该方法可包括:向工艺腔室内通入脱水的氟化氢气体和脱水的醇类气体;使所述脱水的氟化氢气体和脱水的醇类气体混合,生成气态的刻蚀剂;使所述刻蚀剂与所述工艺腔室内的晶片反应,并使所述工艺腔室内保持高压状态以提高刻蚀选择比;以及将所述反应的副产物从所述工艺腔室内抽出。根据本发明的集成电路的制造工艺中,去除晶片上的二氧化硅的方法通过使气态的刻蚀剂在高压力下与二氧化硅直接反应,并在反应后将反应产物抽出,实现高选择比、高效率地去除二氧化硅。

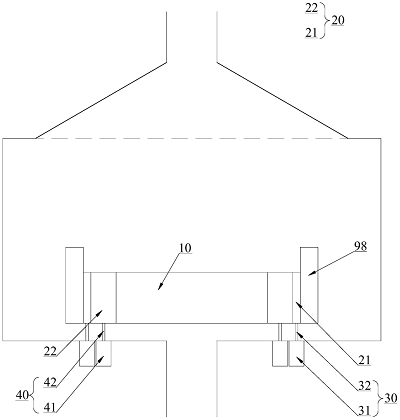

“晶圆卡盘和晶圆加工方法”专利,申请公布日为2024年7月16日,申请公布号为CN118352289A。

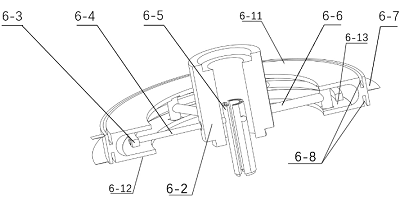

本发明提供了一种晶圆卡盘和晶圆加工方法,涉及晶圆的刻蚀技术技术领域,为解决翘曲的晶圆在等离子刻蚀时易放电打火的问题而设计。晶圆卡盘包括边缘卡盘和中心卡盘,边缘卡盘分布在中心卡盘的至少一个径向的外侧,边缘卡盘传动连接有边缘卡盘驱动装置以调节边缘卡盘的高度。本发明提供的晶圆卡盘能够尽可能的防止晶圆的边缘打火受损。

天眼查显示,芯联集成电路制造股份有限公司“键合结构及其制备方法”专利公布,申请公布日为2024年7月23日,申请公布号为CN118380407A。

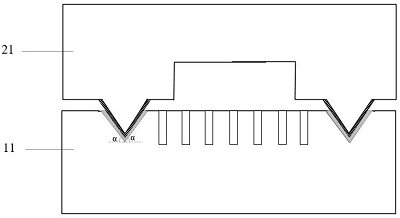

本发明提供一种键合结构及其制备方法,所述键合结构包括:第一晶圆和第二晶圆;所述第一晶圆具有环形凹槽,所述第二晶圆具有环形凸起部,所述环形凹槽具有V型纵截面,所述环形凸起部具有三角状纵截面,所述三角状纵截面的顶角角度与所述V型纵截面的夹角相等;所述环形凹槽的表面覆盖有第一键合层,所述环形凸起部的表面覆盖有第二键合层,所述环形凸起部部分嵌入所述环形凹槽内,使得所述第一键合层和所述第二键合层彼此相键合。

本发明所形成的键合结构,键合层不必为了减小对准偏差而增加尺寸,从而密封环可采用更小尺寸的设计。

天眼查显示,北京忆芯科技有限公司近日取得一项名为“支持SR-IOV的NVMe控制器及方法”的专利,授权公告号为CN112347012B,授权公告日为2024年7月23日,申请日为2016年6月20日。

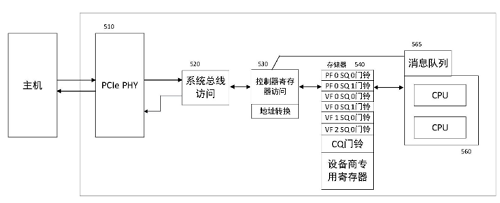

提供了支持SR-IOV的NVMe控制器及方法。其中NVMe控制器包括:系统总线访问部件、控制器寄存器访问部件、CPU以及物理存储器;系统总线访问部件耦合于外部总线并响应于来自系统总线的存储器空间访问请求生成控制器寄存器访问请求,所述控制器寄存器访问请求包括第一存储器地址、访问类型以及PF或VF的标识符;所述控制器寄存器访问部件响应于收到控制器寄存器访问请求,对于访问提交队列门铃寄存器的访问请求,将所述访问提交队列门铃寄存器的访问请求的地址转换为物理存储器地址;所述控制器寄存器访问部件响应于收到控制器寄存器访问请求,对于访问完成队列门铃寄存器的访问请求,将所述访问完成队列门铃寄存器的访问请求的地址转换为存储器地址。

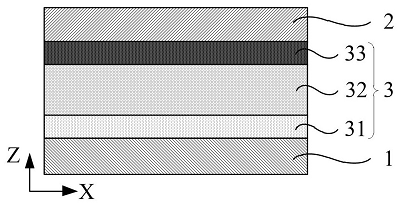

天眼查显示,深圳天狼芯半导体有限公司近日取得一项名为“半导体结构及其制备方法”的专利,授权公告号为CN118198137B,授权公告日为2024年7月23日,申请日为2024年5月16日。

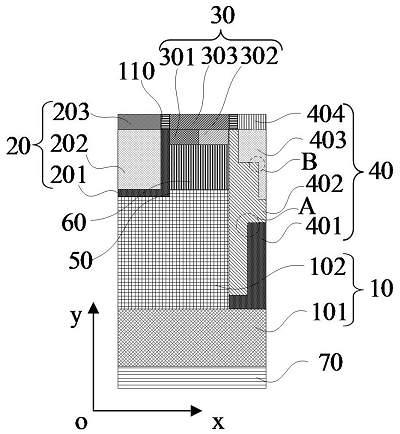

本申请涉及一种半导体结构及其制备方法。该半导体结构包括:基底结构;栅极结构;源极结构;源极场板结构,其中,栅极结构和源极场板结构分别位于源极结构相对的两侧;源极场板结构包括第一阶梯式介质结构、第二阶梯式介质结构、阶梯式场板和场板源电极,第二阶梯式介质结构至少部分和漂移区接触,第二阶梯式介质结构位于第一阶梯式介质结构与阶梯式场板之间,场板源电极在阶梯式场板远离衬底一侧的上表面。

通过将栅极结构和源极场板结构分别设置于源极结构相对的两侧,当器件处于反偏状态时,第二阶梯式介质结构可以调制栅极沟槽内的电场分布,解决了栅极沟槽内因电场集中导致的碰撞电离率升高,进而造成栅极氧化层缺陷的问题。

天眼查显示,广东芯聚能半导体有限公司近日取得一项名为“功率模块外壳”的专利,授权公告号为CN221409385U,授权公告日为2024年7月23日,申请日为2023年11月1日。

本申请涉及一种功率模块外壳,包括壳体、端子组件和保护件,壳体内设有用于容纳内部电路的容纳腔以及与容纳腔连通的走线腔,端子组件穿设于走线腔,且通过走线腔穿入容纳腔内,以与容纳腔内的内部电路电连接,保护件设于走线腔内,且保护件的至少部分位于壳体内壁和端子组件之间,且保护件的弹性模量小于壳体的弹性模量。

当端子组件因环境和温度变化产生应力时,应力先作用在保护件上,保护件会吸收端子组件的应力以及其自身在对应温度条件下产生的应力,即对应应力会先在弹性模量更小的保护件上释放一部分,剩余应力才会继续传递至壳体上,从而能够降低壳体所承受的应力,进而降低壳体开裂失效的风险。

天眼查显示,新美光(苏州)半导体科技有限公司“衬底加热体组件及化学气相沉积设备”专利公布,申请公布日为2024年7月23日,申请公布号为CN118374794A。

本发明涉及一种衬底加热体组件及化学气相沉积设备,其中提供了一种衬底加热体组件,包括衬底和加热体,衬底包括第一表面、第二表面和中空区,第一表面和第二表面均用于供反应气体沉积,中空区位于第一表面和第二表面之间;加热于中空区内,用于产生热量以至少加热第一表面和第二表面。

本发明的衬底设计为内部中空的结构,第一表面及第二表面均为衬底靠近中空区部分的外表面,位于中空区的加热体对衬底的第一表面和第二表面沿径向的各个位置的加热效果相对较为平均,不容易产生沉积的产品厚度差异过大的问题,某些特定的程度上提高了衬底上沉积材料的厚度均一性及组织性能均匀性。

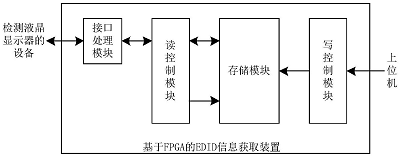

天眼查显示,广东高云半导体科技股份有限公司近日取得一项名为“EDID信息获取装置、液晶显示屏检测装置及方法”的专利,授权公告号为CN116721614B,授权公告日为2024年7月23日,申请日为2023年6月13日。

本申请公开了一种EDID信息获取装置及液晶显示屏检测的新方法,EDID信息获取装置基于FPGA实现,其中存储有至少一个对应分辨率的EDID信息,并且通过上位机更新当前待检测的液晶显示器的分辨率对应的EDID信息,方便快捷地实现了EDID信息的增加或更新。

如此当需要更改分辨率时,只需通过上位机更新确定待检测的液晶显示器的分辨率对应的EDID信息即可简单、快速、方便地切换到需要更改的分辨率对应的EDID信息,提升了对液晶显示屏的检测效率。

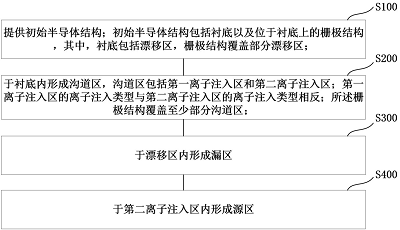

天眼查显示,粤芯半导体技术股份有限公司“半导体结构及其制备方法”专利公布,申请公布日为2024年7月23日,申请公布号为CN118380405A。

本申请涉及一种半导体结构及其制备方法,包括:提供初始半导体结构;所述初始半导体结构包括衬底以及位于所述衬底上的栅极结构,其中,所述衬底包括漂移区,所述栅极结构覆盖部分所述漂移区;于所述衬底内形成沟道区,所述沟道区包括第一离子注入区和第二离子注入区;所述第一离子注入区的离子注入类型与所述第二离子注入区的离子注入类型相反;所述栅极结构覆盖至少部分所述沟道区;于所述漂移区内形成漏区;于所述第二离子注入区内形成源区。在形成沟道区时增加了一道第一离子注入工序,能够尽可能的防止表面沟道产生,减少导通饱和时载流子被硅晶体与氧化层的截面捕获而导致电流无规则起伏的现象发生,降低了闪烁噪声。

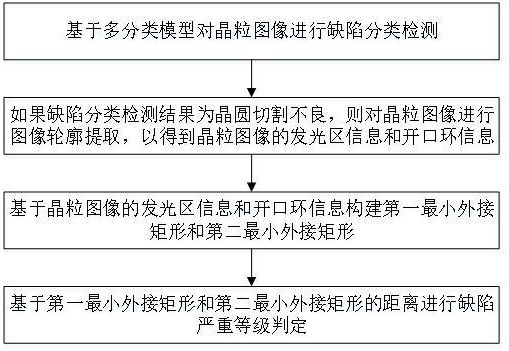

成都数之联科技股份有限公司近日取得一项名为“一种晶圆切割不良缺陷检验测试方法、系统、设备及存储介质”的专利,授权公告号为CN118096767B,授权公告日为2024年7月23日,申请日为2024年4月28日。

本发明提供一种晶圆切割不良缺陷检测的新方法、系统、设备及存储介质,涉及缺陷检验测试技术领域,所述方法流程为:首先基于多分类模型对晶粒图像进行缺陷分类检测,以得到缺陷分类检测结果;如果缺陷分类检测结果为晶圆切割不良,则对晶粒图像进行图像轮廓提取,以得到晶粒图像的发光区信息和开口环信息;然后基于晶粒图像的发光区信息和开口环信息构建第一最小外接矩形和第二最小外接矩形;最后基于第一最小外接矩形和第二最小外接矩形之间的距离进行缺陷严重等级判定,以得到晶圆切割不良等级判定结果。

据悉,本发明采用深度学习和机器视觉相结合的方式进行缺陷检验测试,解决了现有晶圆外观缺陷检测无法对缺陷影响程度进行度量,容易出现过检和漏检的问题。

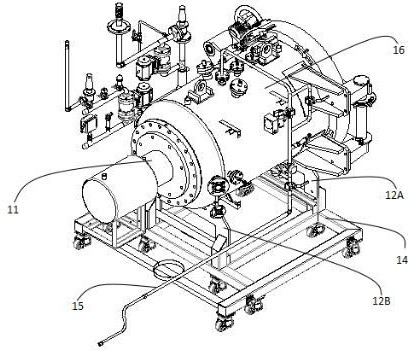

天眼查显示,中科同帜半导体(江苏)有限公司近日取得一项名为“一种芯片真空压力烧结炉”的专利,授权公告号为CN221403859U,授权公告日为2024年7月23日,申请日为2023年10月24日。

本实用新型涉及芯片压力烧结炉技术领域,提供一种芯片真空压力烧结炉,包括炉主体,所述炉主体后方设置有风扇组件,所述炉主体内部设置有加热系统,所述风扇组件用于对所述炉主体内部空气循环,所述风扇组件的下方设置有真空系统,所述真空系统用于对所述炉主体抽真空,风扇组件保证了炉主体的空气流动,保证了炉主体的受热均匀,提高了产品质量。

上海积塔半导体有限公司“极板电容器及其制造方法、半导体结构”专利公布,申请公布日为2024年7月23日,申请公布号为CN118380417A。

本公开实施例提供了一种极板电容器及其制造方法、半导体结构。该极板电容器,包括:在第一方向上相对设置的第一极板和第二极板,以及设置于所述第一极板和所述第二极板之间的介质层;所述介质层包括沿所述第一方向层叠的第一子层、第二子层和第三子层;其中,所述第一子层与所述第一极板接触,所述第三子层与所述第二极板接触,所述第一子层、所述第二子层和所述第三子层的材料组成元素相同,且所述第一子层和所述第三子层中的硅元素含量均小于所述第二子层中的硅元素含量。本公开用于改善MIM电容器的可靠性。

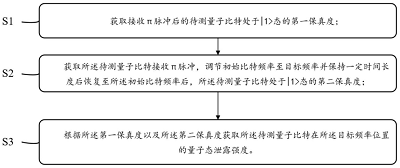

天眼查显示,本源量子计算科技(合肥)股份有限公司近日取得一项名为“量子比特装置量子信息泄露的测试方法及装置”的专利,授权公告号为CN116702910B,授权公告日为2024年7月16日,申请日为2022年2月28日。

本发明提供了一种量子比特装置量子信息泄露的测试方法和装置、量子计算机、可读存储介质,所述量子比特装置量子信息泄露的测试方法包括:获取接收π脉冲后的待测量子比特处于1态的第一保真度;获取所述待测量子比特接收π脉冲,调节初始比特频率至目标频率并保持一定时间长度后恢复至所述初始比特频率后,所述待测量子比特处于1态的第二保真度;

根据所述第一保真度以及所述第二保真度获取所述待测量子比特在所述目标频率位置的量子信息泄露强度。本发明的技术方案能够确定在目标频率位置是否会引发量子信息泄露,进而在做两比特门的过程中,能够设置两比特门的工作点远离这些会引发量子信息泄露的频率位置。

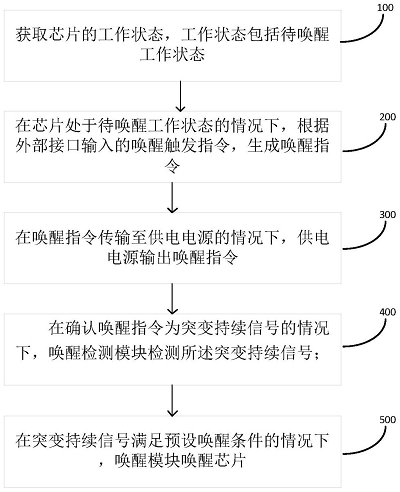

据天眼查信息,深聪半导体(江苏)有限公司近日取得一项名为“芯片唤醒方法、系统、电子设备及可读存储介质”的专利,授权公告号为CN114327651B,授权公告日为2024年7月16日,申请日为2021年12月21日。

本发明提供了一种芯片唤醒方法、系统、电子设备和可读存储介质。该种芯片唤醒方法,应用于芯片唤醒系统,通过获取芯片的工作状态,在处于待唤醒状态时,接收唤醒触发指令,生成唤醒指令,并通过唤醒控制模块将唤醒指令通过芯片的供电电源输出,在确认唤醒指令为满足预设唤醒条件的突变持续信号的情况下,唤醒芯片进入正常工作状态,可以充分利用芯片的有效资源,无需依赖芯片的空闲I/O,实现芯片的唤醒可以在更低功耗模式下实现。

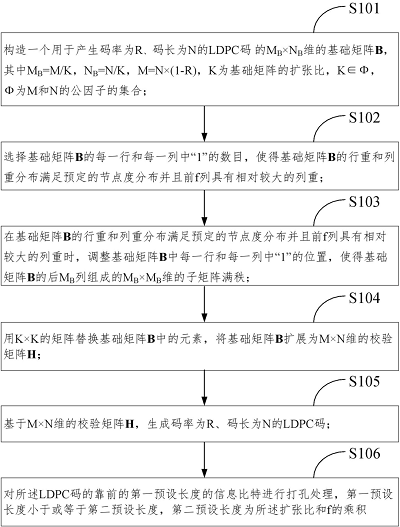

天眼查显示,湖南国科微电子股份有限公司近日取得一项名为“一种LDPC码的构造及编码方法、装置”的专利,授权公告号为CN116436475B,授权公告日为2024年7月16日,申请日为2023年6月13日。

本发明公开了LDPC码的构造及编码方法、装置。所描述的方法包括:构造一个用于产生码率为R、码长为N的LDPC码的MB×NB维的基础矩阵B,MB=M/K,NB=N/K,M=N×(1-R);选择基础矩阵B的每一行和每一列中“1”的数目,使基础矩阵B的行重和列重分布满足节点度分布且前f列具有相对较大的列重;调整基础矩阵B中每一行和每一列中“1”的位置,使得基础矩阵B的后MB列组成的MB×MB维的子矩阵满秩;

用K×K的矩阵替换基础矩阵B中的元素,将基础矩阵B扩展为M×N维的校验矩阵H;基于M×N维的校验矩阵H,生成码率为R、码长为N的LDPC码;对所述LDPC码的靠前的第一预设长度的信息比特进行打孔处理,第一预设长度小于或等于第二预设长度,第二预设长度为扩张比和f的乘积。

摩尔线程智能科技(北京)有限责任公司“内存管理装置、方法、芯片、电子设备”专利公布,申请公布日为2024年7月16日,申请公布号为CN118349483A。

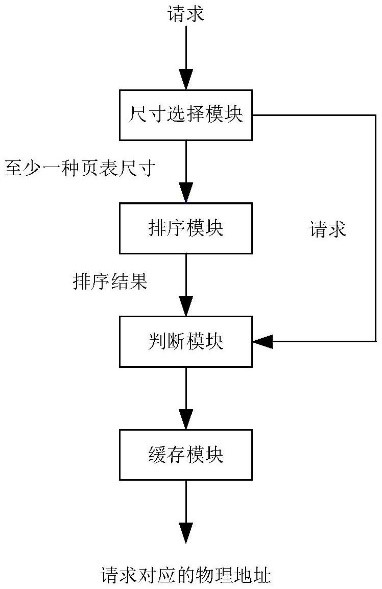

本公开涉及存储技术领域,提出一种内存管理装置、方法、芯片、电子设备。内存管理装置中,尺寸选择模块根据第一请求端的请求得到至少一种页表尺寸;排序模块对至少一种页表尺寸进行优先级排序得到排序结果;判断模块从排序结果中优先级最高的页表尺寸开始,按照优先级从高到低的顺序,判断请求是否命中当前页表尺寸,在请求命中当前页表尺寸时,通知缓存模块以第一预设方式获取与请求对应的物理地址并输出,并结束对请求的命中情况的判断。

该内存管理装置支持多种页表尺寸,在请求命中某一页表尺寸后即可结束对请求是否命中各页表尺寸的判断,在支持较多的页表尺寸的情况下,能够保持比较高的请求响应效率,提升内存管理装置的吞吐量。

*博客内容为网友个人发布,仅代表博主个人自己的观点,如有侵权请联系工作人员删除。

|